ADF4193是AD公司的一款定时IC和时钟产品,ADF4193是低相位噪声、快速建立PLL频率合成器,本站介绍了ADF4193的封装应用图解、特点和优点、功能等,并给出了与ADF4193相关的AD元器件型号供参考。

ADF4193 - 低相位噪声、快速建立PLL频率合成器 - 定时IC和时钟 - PLL/频率合成器 - Analog Devices, LLC

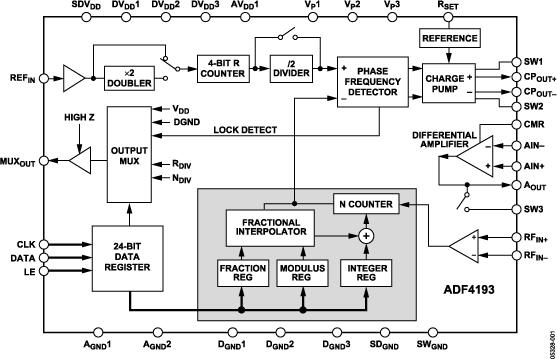

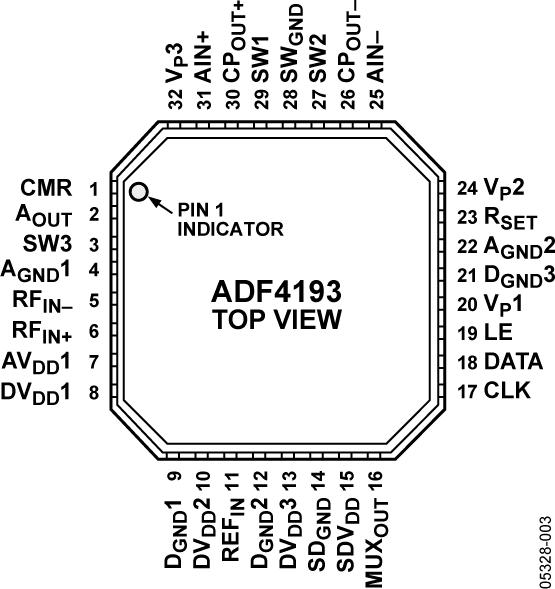

ADF4193频率合成器可以用来在无线接收机和发射机的上变频和下变频部分实现本振,其结构经过特别设计,符合基站的GSM/EDGE锁定时间要求。它由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。

Σ-Δ型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。

应用

- GSM/EDGE基站

- PHS基站

- 仪器仪表和测试设备

该页面包含用于评估ADF4193低相位噪声、快速建立PLL频率合成器的评估板订购信息。

该评估板需使用SDP控制器版以连接PC。SDP控制器板通过USB 2.0连接至PC。评估板将连接至SDP控制器板。评估板无法直接连接至PC。在PC上运行的评估软件通过SDP控制器板与评估板通信。SDP控制器板在以下订购指南中单独列出(EVAL-SDP-CS1Z)。如果以前未购买过SDP控制器板,请购买该产品以确保获得完整的评估设置。

无